Research Interests

- Wireless Security for IoT Systems: RF Fingerprinting, Authentication, and Encryption

- AI-Enhanced RF/Mixed-Signal Circuits for Extreme Environments

- Heterogeneous Integration: Neuromorphic Computing and Embedded Sensing with Emerging Memories and Sensors

- In-Sensor Multimodal Machine Learning

- Compiler Optimization for Heterogeneous Computing Systems

- High-Speed Data Converters (ADCs/DACs)

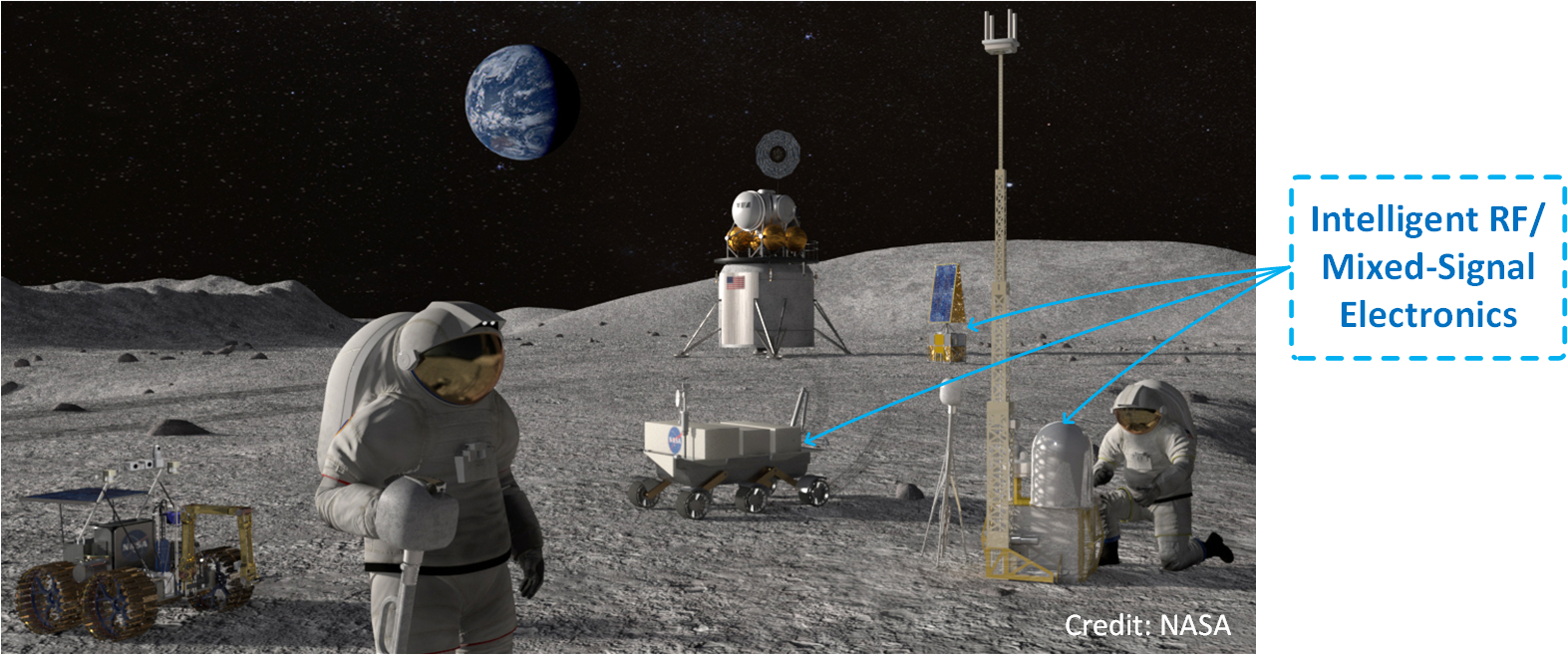

Self-Healing Space Electronics

- Development of self-healing RF/mixed-signal modules for space applications

- Intelligent sensory interfaces performing sensing, feature learning, and communication tasks for in-situ information analysis

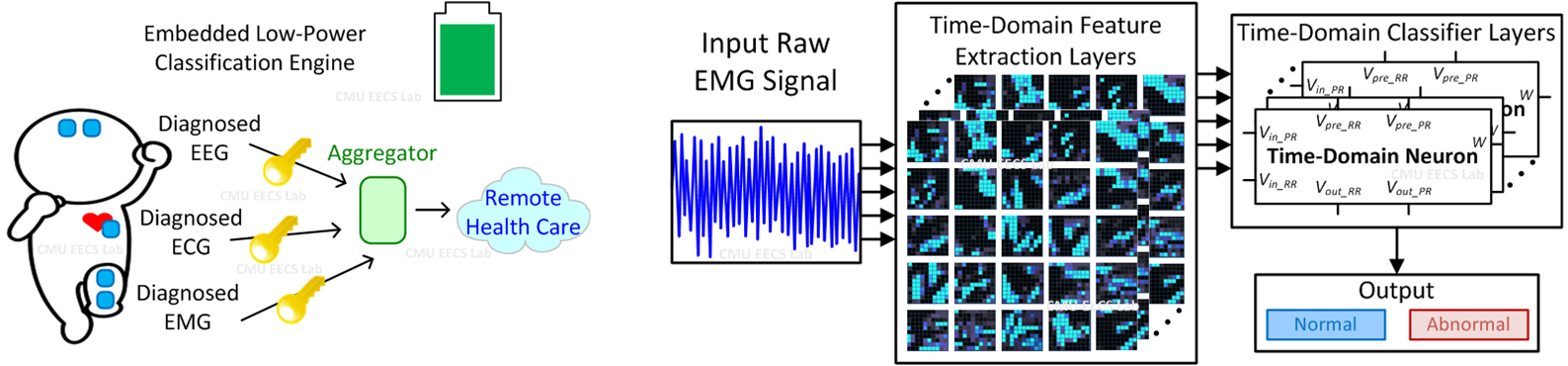

Real-Time Sensing and Computing in Edge Devices

- Critical developments to support big data analysis: ubiquitous sensing/computing, spectrum efficiency and security

- Ultra-low power analog/mixed-signal machine learning classifiers

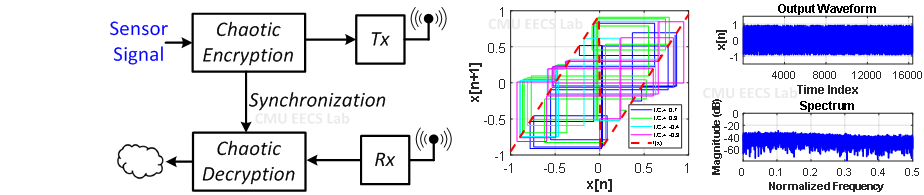

Reconfigurable Chaotic Systems for In-Sensor Encryption

- Unclonable chaotic circuits with non-idealities harvested from the switch-capacitor components

- In-sensor ultra-low power encryption engines to create unobservable patterns to counter side-channel attacks

AI-Enhanced Wireless Transceivers for Secure IoT and Smart Transportation Systems

- Distributed small cells to extend coverage ranges for 5G/6G and beyond

- Trusted transceivers with augmented RF signatures to enable rapid signal identification

- RF physical unclonable function (PUF) incorporating combinatorial randomness

Brain-Machine Interfaces

- Generative-model-based Bayesian neural networks with self-assembly DNA memory and spin-torque oscillators

- Computational neural probes

Previous Achievements

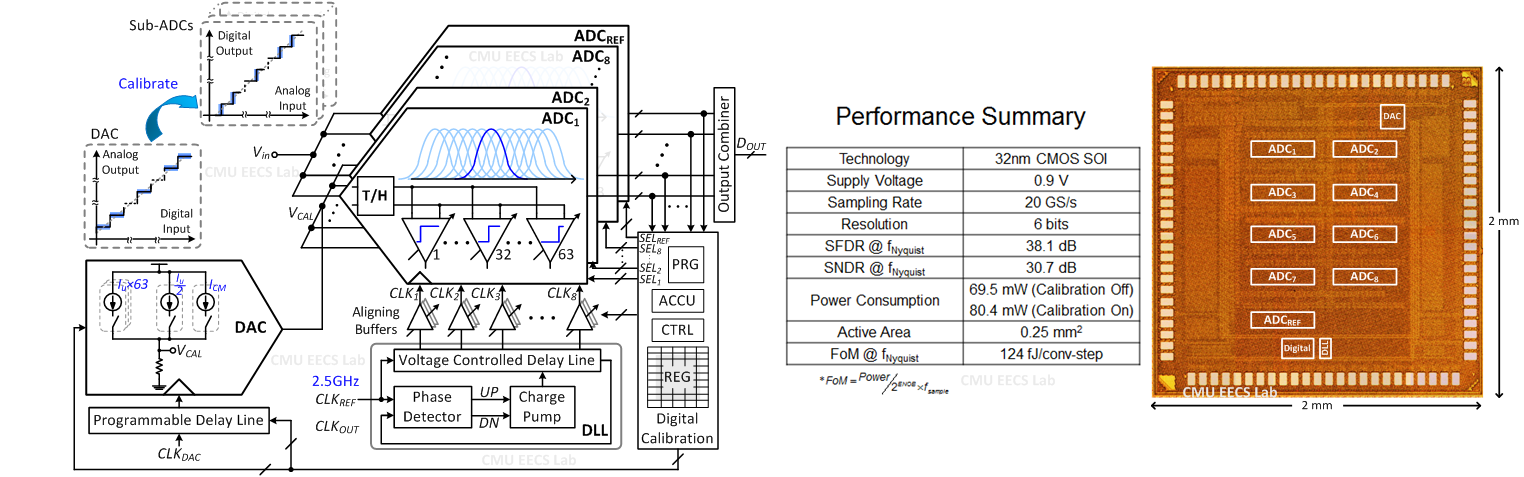

A 69.5mW 20GS/s 6b Time-Interleaved ADC with Embedded Time-to-Digital Calibration in 32nm CMOS SOI

- Near-minimum-size transistors in comparators and clock buffers to achieve low power consumption

- Low-complexity calibration to exploit process randomness for mismatch compensation without full rate clock of 20GHz

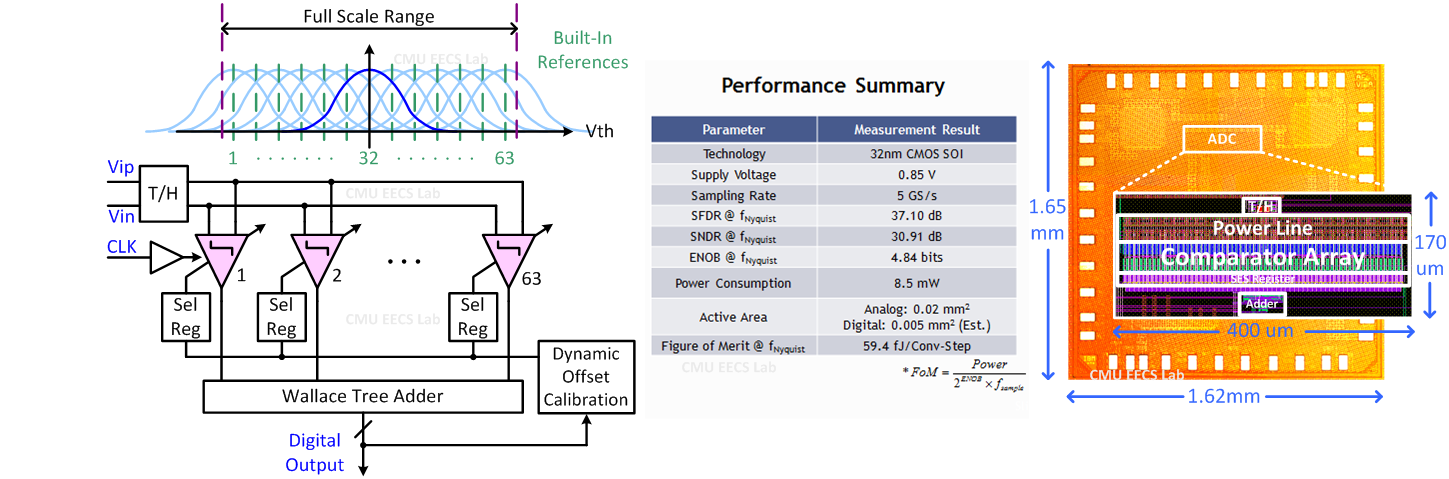

An 8.5mW 5GS/s 6b Flash ADC with Dynamic Offset Calibration in 32nm CMOS SOI

- Near-minimum-size transistors in the design and elimination of usage of the resistor ladder as reference levels

- Utilization of dynamic offset calibration to compensate for process variations including static and dynamic errors

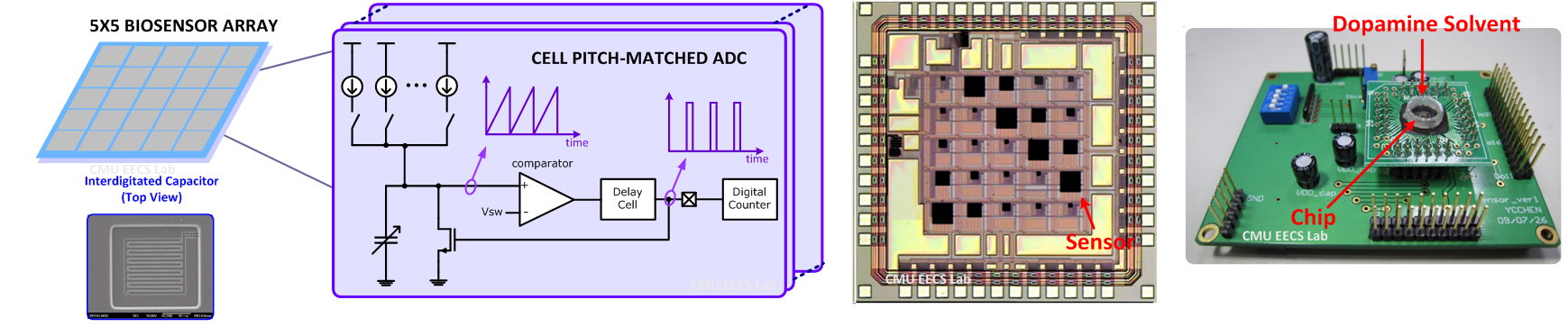

CMOS Capacitive Sensor Array for Detection of the Neurotransmitter Dopamine

- Cell-pitch ADCs to enable parallel readout to reduce scan time for biomedical applications

- Fully integrated biosensor array with power/area-optimized ADC design to avoid signal degradation