#### Welcome!

- We had a good year...

- We'll tell you about it

- Discuss how to best use what we have done

- Discuss how to make it better

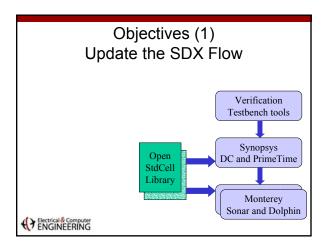

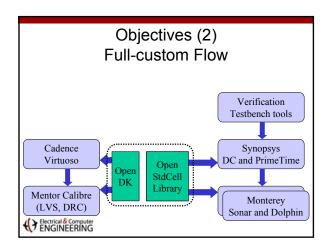

- We are expanding our goals...

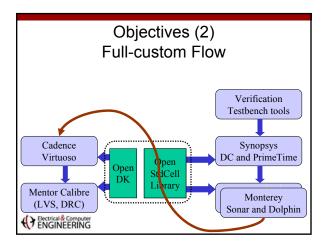

- Full-custom VLSI design (layout)

- New Design Kits, consolidating existing ones

- Organized way to capture design flow knowledge

- We need feedback to increase impact

#### Sandbox Mission

- Developing, sharing, supporting CAD tool flow

- Graduate design classes (Sandbox Design Experience Class)

- Advanced Undergraduate Classes

- PDG Short Courses

- Research

- Providing Technology for Collaborative Design

- Sandbox Design Experience Class

### My New Idols

- CIC in Hsinchu, Taiwan

- http://tn-www.cic.org.tw/en/

- Design flow development, support (and testing!)

- Every tool obtainable from CAD tool vendors

- Training using tools (7462 students/year!)

- Multi-chip Wafer Fabrication (300 designs/year!)

- Chip testing facilities (test chip, or no more fab)

- I wish we could do this all

- CIC has a budget of \$45M and a staff of 40 people

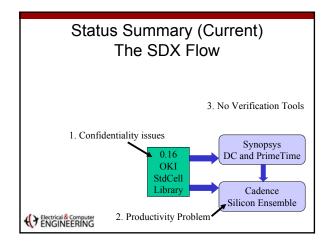

# Status Summary (Current) The SDX Flow Synopsys DC and PrimeTime OKI StdCell Library Cadence Silicon Ensemble ENGINEERING

## Who's using Sandbox

- Greg Link , PennState ECE

- Network-on-Chip research

- ASIC Flow(Synopsis, Cadence); OKI Libraries and memories

- Ricky Radaell-Sanchez, CMU ECE

Network-on-Chip LDPC decoder chip

ASIC flow (Synopsis, Monterey), STMicro library

Theo Theocharides, PennState ECE

- - Neural network face detector

- ASIC flow (Synopsys, Cadence); OKI library and memories

- Others using FPGA tools, Synopsys for area estimates, Cadence generic PDK analog design, NCSU PDK for AMI 1.6u

## **Tech Library Complications**

- NDA: No Design Allowed?

- TSMC, ST:

- No educational use

- Specific research use

- OKI

- Abstract views only

- SCMOS based

- Not very tech specific

- No memory generators, etc.

Electrical & Computer ENGINEERING

## Agenda

- Full austom design flow (Max Khusid)

- Better semi- austom design flow (Herm and Tom)

- Sandbox Website and CADFAQ (Max)

- Discussion and Wrapup

- Dave: Synergy between Sandbox flow and short courses

- Promotion of CADFAQ

- Other topics?

ENGINEERING

#### Feedback

- We can't do everything

- Big new things

Examples: Analog Artist, NeoCell, etc.

- Realize that these may take some time

- Small adjustments

- Things that we can do that make what we're doing more useful

New class requirements

- Making our job easier

Things that we can utilize now

Reducing duplicated effort

Electrical & Computer ENGINEERING