Electrical & Computer

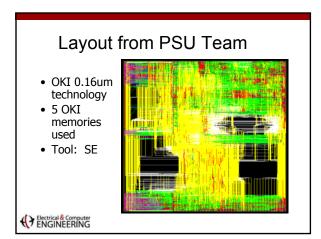

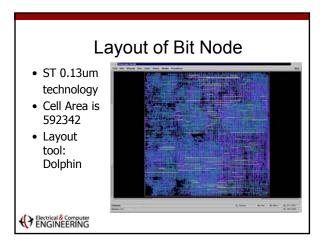

Layout from CMU1 Cnode Team

OKI 0.16um technology

3 OKI memories

Tool: Silcon Ensemble

### 1

Electrical & Computer

RTL Generation

Synthesis

(Synopsys)

Electrical & Computer

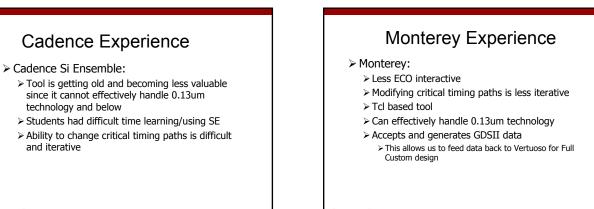

# What we're doing to build this

- Student building "Best of SDX" in ST 0.13

- Using Monterey for full chip design

Electrical & Computer

Electrical & Computer

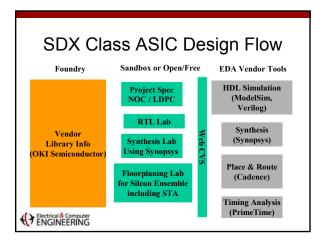

Proposed Design Flow

GDSII, LEF, or MTF data (ST, CMUlib18) Dolphin / Seascape

(Monterey)

LEF

STA (PrimeTime) DEF

.sdf

GDSII

MTF

ST 0.13um,

CMULib18

(.v's, .sdf's)

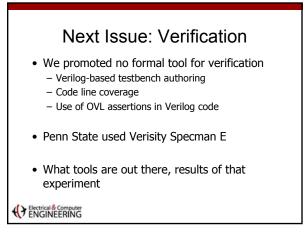

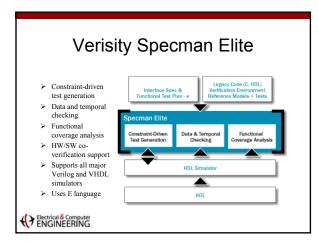

# Synopsys Vera

- Easy to learn

- > Next Gen. Constraint solver finds bugs quickly

- Formal analysis engine

- $\succ\,$  Supports re-use across projects, geographies, and teams

- > Uses VHDL, Verilog, and SystemC

- Access to OpenVera Verification IP

#### Electrical & Computer

#### Open Vera

- > OpenVera is an open hardware language

- Seamless tool integration and open distribution of verification IP.

- Goal is to establish a hardware verification language (HVL), called OpenVera™,

- Easy to learn

- Combines the strengths of HDLs, C++ and Java

- Additional constructs for functional verification making it ideal for developing testbenches

- OpenVera accelerates verification by providing high-level constructs designed for complex SoCs.

- Designers create testbenches using OpenVera and EDA vendors create tools that are interoperable.

Electrical & Computer

# SystemVerilog

- Language structures for assertions

- Not yet accepted into tools...

Electrical & Computer

# Discussion

- Functional Verification tools:

Good tools?

- Falsely perceived silver bullets?

- Satisfied with Verisity for Verification Class?

# New Libraries

- Plan to using CMU18Lib

- One technology library across the curriculum

Full Views

- DRC, LVS, etc

- Can be fabricated with MOSIS on TSMC

Electrical & Computer

ENGINEERING

## Problems/Issues with Libraries

- Memory Generators!

- Nobody gives these out

- Need: LEF, Liberty

- Like to have: GDSII (unlikely)

- May enlist undergraduates

- IOs / PLLs / Passives

# SDX Class Improvements

- How did this class work?

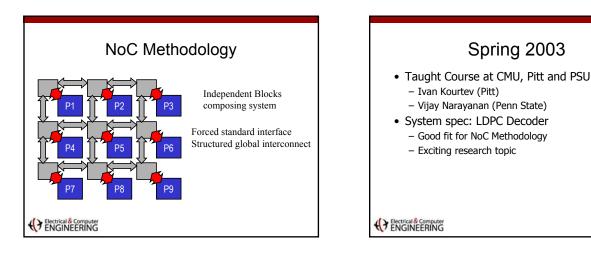

- Network-on-Chip

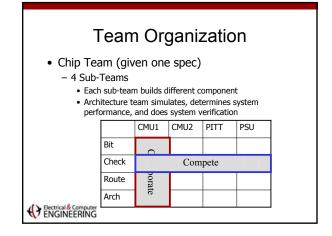

- Team organization

- · What could have been better?

- What should be the design objective this year?

#### Electrical & Computer

Electrical & Computer

#### **Requirements for Success**

- A Firm Specification of Design

- · Something that gets students excited

- A Passionate "Consumer"

- PipeRench was successful

- picoJava was not

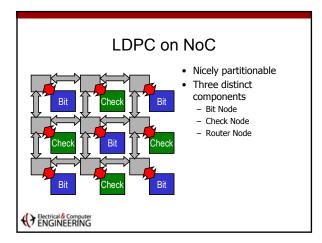

- I think LDPC on NoC was successful

#### Industry Challenges to SoC Design

- Divide and conquer (hierarchy)

- Reduce the atomic problem size

- Improve the correspondence of wireload models

- Allow multiple teams to work independently

Reduce time to market

- Design Re-use

- Design Re-use

- Decoupling of efforts

Specified Interfaces

- Clear Match of Responsibilities and teams

Electrical & Computer

# Industry < Education

- Design Productivity is in crisis

- Issues are even worse in academia

- Semester less than product design cycle

Reality: less than a semester

- Reality: less than full-time

- Divide and conquer is even more important

Senioritis

- Can't adjust if team doesn't have right skills

Failure is an option, but we still have to give a grade

#### Electrical & Computer

Electrical & Computer

# Network on a Chip Design

- Hot and Hip Topic in Industry

- Great for education

- Highly decoupled design

- Structured interfaces

- If some team blows it off, still can evaluate others

- Good results:

- Most teams successfully tested their componentTwo of four chip designs passed some whole chip test

# CMU Results

- We had one flunky subteam

- Bad personality mix

- Two hard workers, two bums

- Their problems didn't poison the well

- Good load balancing

- Arch teams worked hard on verification

- My best Faculty Course Evaluation ever

#### Electrical & Computer

# **Class Organization**

- Right size design teams?

- Expected enrollment the same?

- Design review structure?

Electrical & Computer

# New Class Design

- Re use NoC Methodology?

- Could re use the existing design specs? – Cheating? / Novelty?

- Substantially Modified Spec?

- Change the network topology?

- Make it substantially bigger?

- Make the processors more general purpose?Ideas from research?

- Could attempt to develop a new app in NoC

A lot of effort

Electrical & Computer

# **Class Logistics**

- Conference Call Phone was not ideal

- Students are not aware of mikes

- Repeated questions... repeated answers...

- We are planning to upgrade our classroom

- Other conferencing issues?

Electrical & Computer

# Class To Do List

- Schedules:

- Do we have the same issues this year?

- Verilog:

- Pitt and PSU get VHDL, learning Verilog was hardBetter labs

- Planning session in October...