## **CMULib18 Motivation**

#### ➤ Legal issues with commercial libraries

- Obtaining std.cell libraries is a lengthy process

- Commercial libraries require NDA's every semester and by both students and faculty

- Legal differences in education or research use

#### > Technical Limitations of commercial libraries

- Typically, no or limited technical support provided

- No full views (no layouts, schematic, etc)

- Can't be extended for easily extended for research purposes

### CMUlib18, Credits

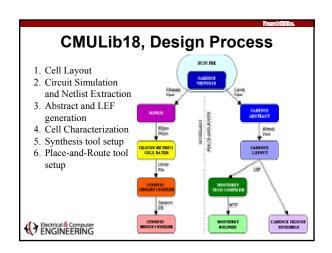

#### > CMULib18 completed over the summer

- First revision, more to come

- Build on a SCMOS-based "open" design kit

#### > Project Lead

- Andrzej Strojwas and Herman Schmit

- ➤ Cell Layout and Characterization

- Zack Menegakis and Steve Beigelmacher

- > CAD Support, LEF, Monterey Dolphin

- Max Khusid and Tom Kroll

## CMULib18, at a glance

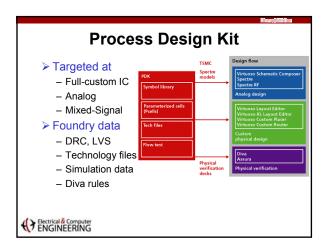

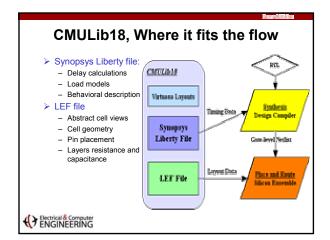

#### TSMC 0.18um, SCMOS DEEP

- Bsim3v3 SPICE models are taken from MOSIS

- 6-metal process

#### > Development Process

- Cell layouts were done in Cadence Virtuoso

- Built using NCSU PDK (DRC, LVS, ETC, layers defs)

#### ➤ Current Status

- Contains 35 most commonly used cells

- Integrated with synthesis and P&R tools

- Capable of going through entire RTL-to-GDSII design flow

# CMULib18, Cell List

- > Primitive: INV, BUF, TRIINV, TRIBUF

- 1, 2, 4, 8x strength for INV and BUF

- > Basic gates: AND, OR, NAND, NOR, XOR, XNOR

- Multi-input (2,3,4)

- 1x strength

- Complex gates: OAI, AOI, MUX

- > Sequential: Latch, DFF

- Scanned and Regular

- With and without Clear

#### > Future Releases

more FFs, I/O Pads, Clock buffers, more drive strengths

Other Public Libraries

- ➤ VirginiaTech Standard Cell library (VTVTLib25)

- SCMOS 0.25um (DEEP SUBMICRON rules), NCSU PDK

- Integrated with Silicon Ensemble and Design Compiler

- Approx. 40 cells, layouts provided

- Free for universities and non-profit organizations

- > Cadence Standard Cell library (GSCLib)

- Demo library, still work in progress

- Appears to be based on 0.18um process

- Works with Cadence Generic PDK

- > Illinois Institute of Technology library

- TSMC 0.25/0.18 (SUBMICRON SCMOS rules)

All Libraries are installed on AFS under Sandbox project tree.

Electrical & Computer ENGINEERING

Sandbox, Big Picture

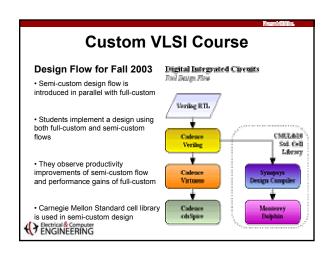

## SEMI-CUSTOM DESIGN FULL CU

- CAD Tools

- ModelSim

- Design Compiler

- Silicon Ensemble

- Monterey Dolphin

- Verisity Specman

- Std. Cell LibrariesCMULib18

- STMicro 0.09,0.18,0.13

- OKI 0.16

- Cadence GSCLib

- VTVTLib25

#### **FULL CUSTOM DESIGN**

- CAD Tools

- Cadence Virtuoso

- Cadence ICFB suite

- Hspice

- Calibre

- Process Design Kits

- NCSU CDK (SCMOS for TSMC, AMI, HP)

- Cadence Generic PDK

- STMicro 0.09 0.18

- TSMC

### **Goals and Discussion**

- > Help with Cadence Virtuoso Installation

- ECE facilities understands Cadence under AFS

- ➤ Consolidate Design Kits

- Who has NDAs for what libraries?

- Is it beneficial to keep them all in one place?

- ➤ Install the 0.18µ Design Kit and CMU18Lib

- > Provide quick start labs for full custom design

- ➤ Needs:

- The contact for PSU and Pitt?

- Timeframe? When is undergrad VLSI taught?

Electrical & Computer ENGINEERING