| Sandbox                | CAD Support            | , 1 <sup>st</sup> year |

|------------------------|------------------------|------------------------|

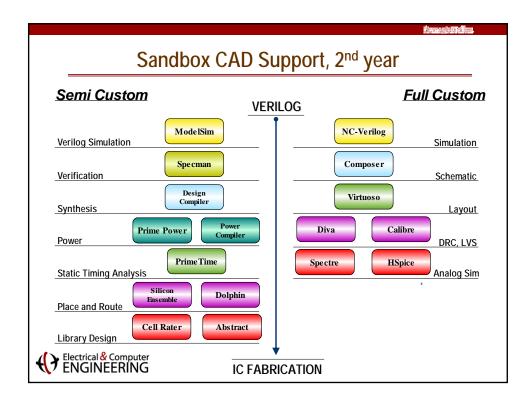

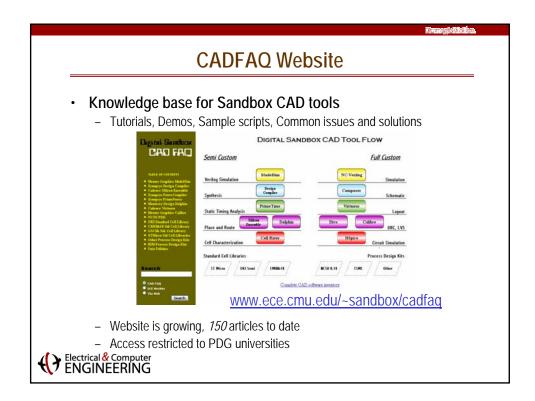

| Semi Custom            | VERILOG                | Full Custon            |

| Verilog Simulation     | m                      | NC-Verilog Simulation  |

| Verification           | n                      | Composer Schematic     |

| Synthesis Design       |                        | Virtuoso               |

| Power Prime Power      | Power<br>Compiler Diva | Calibre DRC, LVS       |

| Static Timing Analysis | me Spectr              | HSpice Analog Sim      |

| Place and Route        | Dolphin                |                        |

| Library Design         | Abstract               |                        |

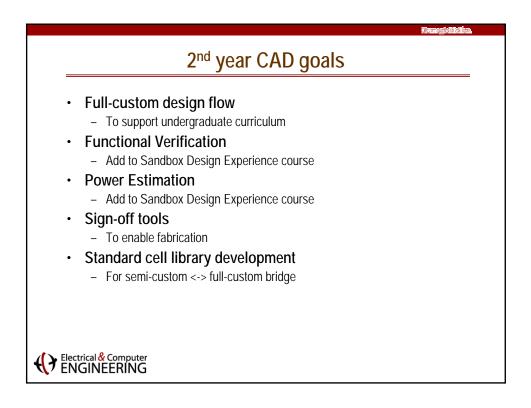

| <u>Semi Custom</u>                                  |                      |                 | Full Custon     |

|-----------------------------------------------------|----------------------|-----------------|-----------------|

| Verilog Simulation                                  | ModelSim             | NC-Verilog      | Simulation      |

| Verification                                        | ecman                | Composer        | Schematic       |

| Synthesis                                           | Design<br>Compiler   | Virtuoso        | Layout          |

| Power                                               | me Power<br>Compiler | Diva            | ibre DRC, LVS   |

| STA                                                 | Prime Time           | Spectre         | pice Analog Sim |

| Place and Route                                     | Silicon<br>Ensemble  | Taurus Sal      | ber TCAD        |

| Testing                                             | Test TetraMax        |                 | FPGA            |

| Library Design<br>ectrical & Computer<br>NGINEERING | ell Rater Abstract   | Synthesis & P/R | Xilinx ISE      |

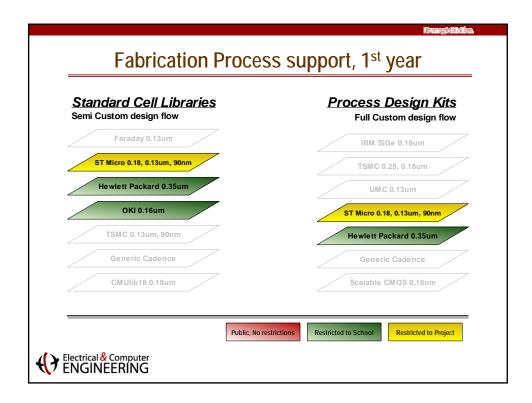

| Standard Call Library Com                    | orioon          |                      |                 |                                |

|----------------------------------------------|-----------------|----------------------|-----------------|--------------------------------|

| Standard Cell Library Com                    |                 | Girish Venkat        | aramani   Answe | red: Max Khusid   Date: 03/11/ |

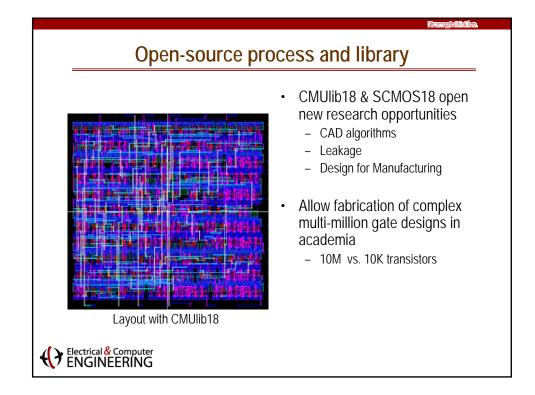

| Sample design: LDPC decoder for              | 6x9 H-matrix, a | approx 100           | ),000 gates, 1  | 5ns clock period.              |

| Std. Cell Library                            | Area, sq. um    | Slack, ns            | Power, mW       | Equivalent Gate area, un       |

| Commercial 0.16um                            | 1,245,281       | 2.17                 |                 | 1.56 x 5.2 = 8.112             |

| CMUlib18 2003, SCMOS 0.18um                  | 966,488         | 4.84                 | 220 + 0.0       | 1.44 x 6.48 = 9.3312           |

| CMUlib18 2004, SCMOS 0.18um                  | 746,113         | 8.40                 | 227 + 0.0       | 1.44 x 6.48 = 9.3312           |

| GSClib                                       | N/A             | 7.46                 | 721 + 0.0       | 2.64 x 7.92 = 20.99            |

| Commercial 0.18um                            | 549,797         | 7.71                 | 268 + 0.0       | 1.28 x 6.40 = 8.192            |

| Commercial 0.13um                            | 279,297         | 6.70                 | 105 + 6.8       | 0.82 x 4.92 = 4.0344           |

| Commercial 0.09um                            | 165,718         | 6.30                 | 71 + 0.15       | 0.56 x 3.92 = 2.1952           |

| <ul> <li>It's be</li> <li>Speed a</li> </ul> |                 | e commer<br>an be im | proved          | vorse than the other<br>ayout  |

| • In | expensive                                                              |

|------|------------------------------------------------------------------------|

| _    | Pros: NetMeeting plus Webcam, cheap \$100-500 webcams                  |

| _    | Cons: very poor quality, can't see students, and hard to interact      |

| • 0  | utsourcing                                                             |

| _    | CMU's IT group, \$200 for 1 <sup>st</sup> hour, \$50 for additional    |

| -    | SDX course: 6 design reviews + 6 lectures = \$2000                     |

| -    | Pros: no hassle                                                        |

| -    | Cons: temporary solution, fixed locations (UC)                         |

| • Pr | ofessional, in-house                                                   |

| -    | DV camcoder(\$1500), cameraman (we can do)                             |

| -    | Real-time codec server, price? 3-way video? Separate ISDN?             |

| -    | Might need professional assistance with setup                          |

| -    | Pros: state-of-the-art, promote interaction, shared with other classes |

| -    | Cons: price, \$5000 – \$20,000                                         |

|                                                              | Brungh Billin.                                                                             |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Modern tools – Mo                                            | odern challenges                                                                           |

| Semi Custom                                                  | <ul> <li>State-of-the-art CAD tools<br/>allow to stay in touch with</li> </ul>             |

| Verilog Simulation ModelSim                                  | modern semiconductor<br>trends                                                             |

| Synthesis<br>INDUSTRY<br>STANDARD<br>Prime Power<br>Compiler | <ul> <li>Challenges addressed:</li> <li>Code coverage</li> </ul>                           |

| Static Timing Analysis                                       | <ul> <li>Assertions</li> <li>P/R of millions of gates</li> <li>Signal integrity</li> </ul> |

| Place and Route Ensemble Encounter                           |                                                                                            |

|                                                              |                                                                                            |

| Semil Custom BREADTH Full Custom<br>Verlog Simulation<br>Verlog Verlog Simulation<br>Verlog Verlog | <ul> <li>Elaborate design flows<br/>improve design <i>quality</i> and</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Synthesis         Design<br>Length         Variance           Power         Perger         Difficult         Difficult           State         Power         Perger         Difficult         Difficult                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | credibility                                                                      |

| Silino<br>Place and Roule         Pion           Place and Roule         Textman           Incommer<br>Testing         Textmax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Examples:                                                                        |

| Library Design Cell Rater Alstract Symplify XIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>Sign-off quality timing</li> </ul>                                      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | – Transient power                                                                |

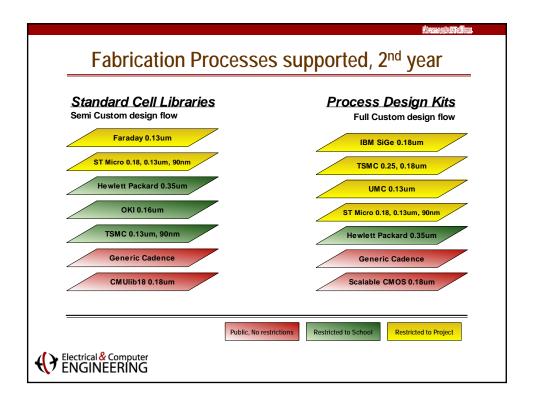

| Standard Cell Libraries         Process Design fits           mit Custom design flow         Fuil Custom design flow           Yaraday 0.13mn         BM Sile 0.15mn           Micro 0.11, 0.12mn, Shim         TBM C0.25, 0.14mn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | – Custom libraries                                                               |

| Hewisti Patari 0.25km MIC 0.413m MIC 0.413m ST Micro 0.16, 15 Micr                                                                                                                                                                              |                                                                                  |

| Student and Advisor                | Research project             | Sandbox support               |

|------------------------------------|------------------------------|-------------------------------|

| S. Rovner & Prof. Pileggi          | Via-Patterned Gate Array     | Design Kit, Cadence           |

| Y. Takegawa & Prof. Strojwas       | Design for Yield             | Software installs and support |

| Z.Menegakis & Prof. Strojwas       | Design for Manufacturing lib | Cell library development      |

| C.Hao & Prof. D. Marculescu        | Low-power design             | ASIC CAD support              |

| J. Hu & Prof. R. Marculescu        | Low-power, leakage           | Power Compiler, ASIC, libs    |

| Prof. J.C. Hoe and Pueschel        | Hardware DSP Automation      | ASIC CAD support, libs        |

| Prof. Mukherjee                    | Classwork and MEMS           | Design Kits                   |

| T. Zanon & Prof. Maly              | Design for Yield             | TCAD tools, memory layout     |

| T. Theocharides & Prof. Narayanan  | Neural Networks              | OKI libs, ASIC CAD            |

| A. Hermawan & Prof. R. Marculescu  | Interconnect & parasitics    | Cadence, Diva                 |

| G. Venkataramani & Prof. Goldstein | Asynchronous HW              | ASIC CAD, Encounter, libs     |

| J. Park & Prof. Yue                | High-speed analog design     | Design kit and libs           |

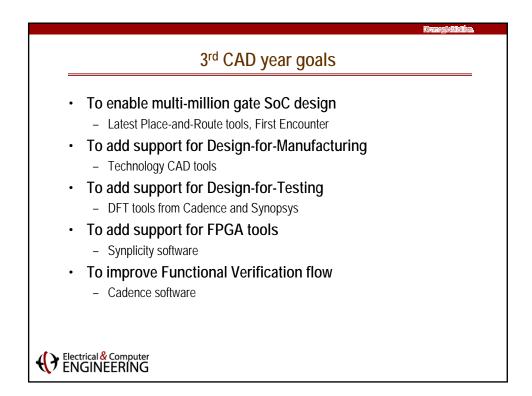

## Sandbox support for Education

- · Past year Sandbox supported three courses

- Undergraduate custom VLSI course (18-322), CMU

- Graduate semi-custom VLSI courses, SDX, CMU/PSU/PIT

- Graduate custom VLSI course (18-525), CMU

- In 2004, updated undergraduate custom VLSI course

- Introduce semi-custom design in a junior-level course

- Next year, possible candidates include

- Undergraduate Functional Verification course, CMU

- Undergraduate Hardware design methodologies course, PIT

- Undergraduate Verification course, PITT/PSU

- Graduate testing course, CMU

Electrical & Computer